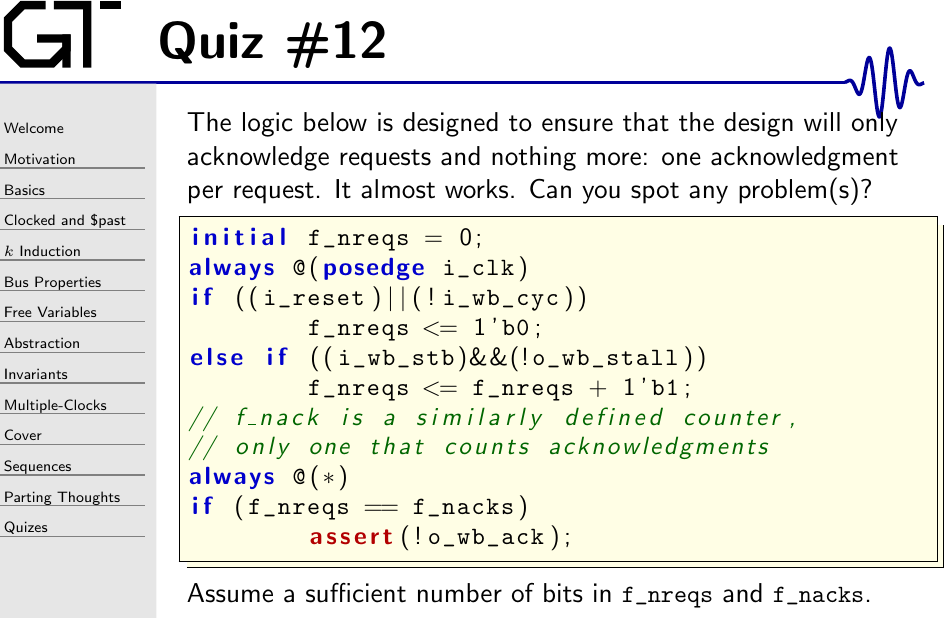

Quiz #12: Catching extraneous acknowledgments

|

Click here for the answer.

I generally insist on four generic bus properties when building a property set for a new bus interface:

-

The bus must return to idle following a reset. This includes resetting any internal counters.

-

If the bus is ever stalled, the stalled request (or response in the case of AXI) must not change.

-

Every request must get a response. This was the bug I found in Xilinx’s IP–requests might never get responses [1] [2]. They’ve promised fixes in Vivado 2020.1, but that’s been a long time in coming now. Intel’s demonstration core is similarly broken.

-

The slave shall not issue any responses without a prior request. This was another of Intel’s AXI3 bugs.

Today’s quiz focuses on the last of these generic properties.

To know if a bus response hasn’t been requested, you need to count up all the requests and similarly count up all the responses. If all requests have been responded to, then there shouldn’t be any further responses.

There’s a subtle exception to how this logic plays out that’s specific to any Wishbone (pipelined) implementation. Check out this post for a hint at what the answer might be. AXI doesn’t have this problem, and this approach wouldn’t be appropriate for Wishbone classic since Wishbone classic doesn’t permit outstanding requests in the first place.