Answer to Quiz #19

|

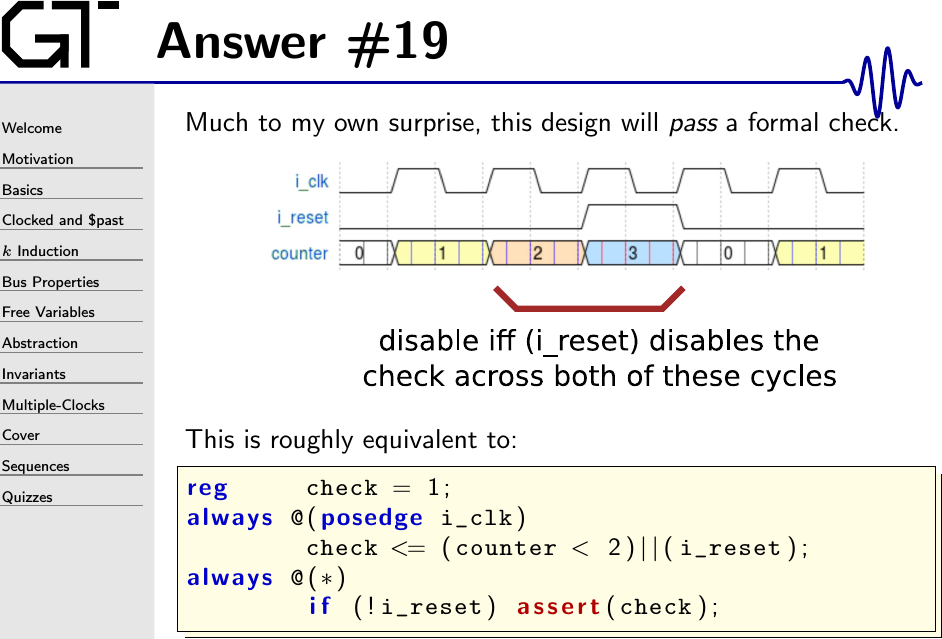

The key to understanding this quiz question is a bit of an understanding of

how things work under the hood. disable iff disables the check on any

cycle of the sequence, to include the cycle when the check takes place!

Further, when doing an assertion @(posedge i_clk), the check takes place

on the clock edge following the failure.

So let’s walk through this. A check function takes place for the assertion,

as shown above.

That function catches the assertion failure when the counter equals two.

However, the check acts like a registered variable–because the assertion only

takes place @(posedge i_clk), so it’s not asserted until the clock cycle

after the failure. On this cycle, the reset is high, so the check isn’t

active.