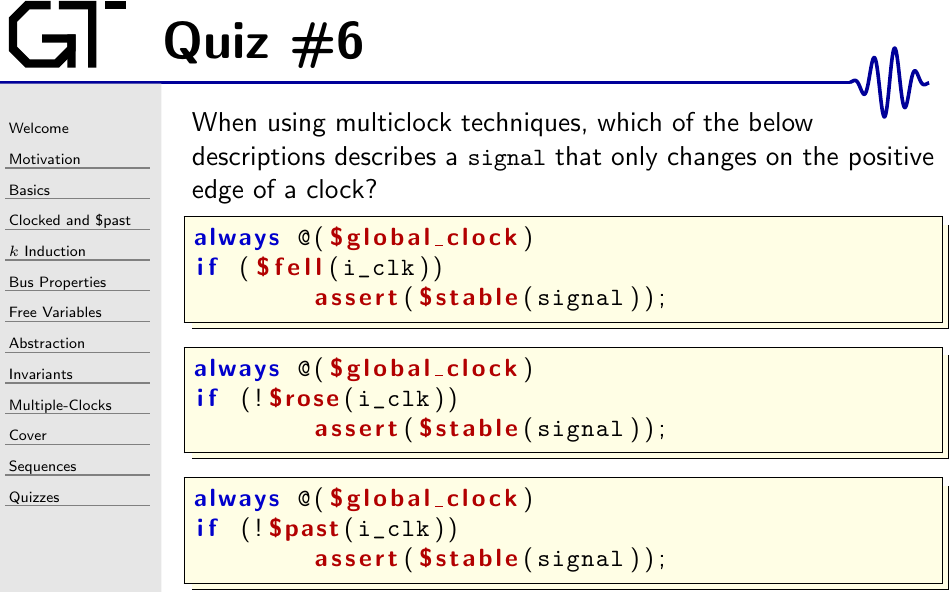

Quiz #6: Synchronous logic in Asynchronous contexts

|

Click here for the answer.

This quiz is really intended for the open version of SymbiYosys. The

open Yosys doesn’t quite implement $global_clock properly. According to

the SystemVerilog standard, $global_clock is supposed to be a clock

chosen by the designer to be the default clock thoughout the design any

time a default clock is necessary throughout an entire design, rather than

(as used here) one that is set by the tools to be a formal time step.

As a result, the reference to $global_clock as used above has been

deprecated. I also expect this non-standard usage to be removed soon enough.

To fix this issue, Yosys now supports the attribute (* gclk *) to define

a wire or register that will contain the formal timestep. You can then use

edges of such a register, rather than $global_clock, to specify the

formal timestep.

(* gclk *) reg gbl_clk;

always @(posedge gbl_clk)

assert(...);Were you using concurrent assertions, the design should read:

(* gclk *) reg gbl_clk;

assert property (@(posedge gbl_clk)

$fell(i_clk) |-> $stable(signal);

assert property (@(posedge gbl_clk)

!$rose(i_clk) |-> $stable(signal);

assert property (@(posedge gbl_clk)

!$past(i_clk) |-> $stable(signal);That said, only one of these captures the logic check desired. Can you tell which one?