### 4. Pipeline Control

Gisselquist Technology, LLC

Daniel E. Gisselquist, Ph.D.

### **G** Lesson Overview

#### Objectives

LED Walker

▷ Lesson Overview

- Diagrams

- Pipeline

- Bus

- Wishbone Bus

- Simulation

- Unused Logic

- Sim Exercise

- Past Operator

- Formal Verification

- SymbiYosys Tasks

- Exercise

- Bonus

- Conclusion

- State diagrams

- Pipeline control structures

- Minimal peripherals

- Simulating Wishbone

- **\$past()** operator

- Verifying Wishbone

## GT LED Walker

| Lesson Overview     |

|---------------------|

| ▷ LED Walker        |

| Diagrams            |

| Pipeline            |

| Bus                 |

| Wishbone Bus        |

| Simulation          |

| Unused Logic        |

| Sim Exercise        |

| Past Operator       |

| Formal Verification |

| SymbiYosys Tasks    |

| Exercise            |

| Bonus               |

| Conclusion          |

|                     |

### Let's make our LED's walk on command

- Bus requests

- State Diagram

## G Goal

| Lesson Overview     | L |

|---------------------|---|

| ▷ LED Walker        |   |

| Diagrams            |   |

| Pipeline            |   |

| Bus                 |   |

| Wishbone Bus        |   |

| Simulation          |   |

| Unused Logic        |   |

| Sim Exercise        |   |

| Past Operator       |   |

| Formal Verification |   |

| SymbiYosys Tasks    |   |

| Exercise            |   |

| Bonus               |   |

| Conclusion          |   |

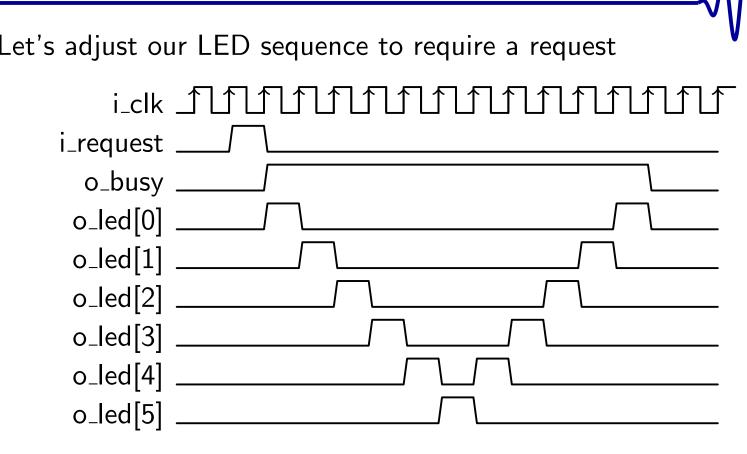

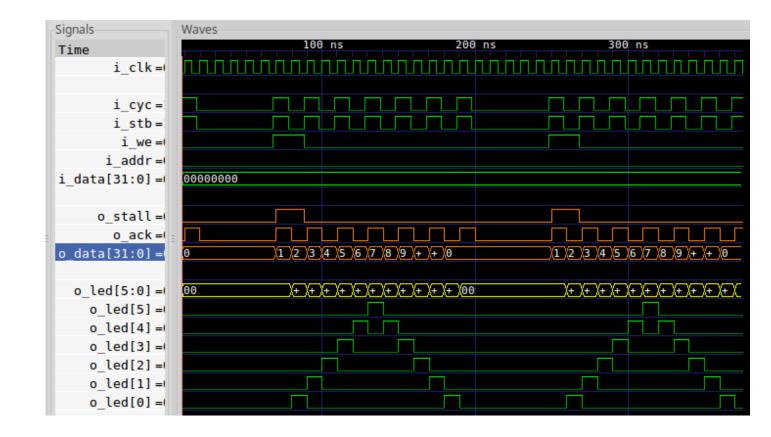

$\hfill\square$  Our goal will be to create a design with these outputs

If successful, you'll see this in GTKwave

## Goal

| Lesson Overview<br>▷ LED Walker<br>Diagrams<br>Pipeline<br>Bus<br>Wishbone Bus<br>Simulation<br>Unused Logic<br>Sim Exercise<br>Past Operator<br>Formal Verification<br>SymbiYosys Tasks<br>Exercise<br>Bonus<br>Conclusion | We'll add state ID's to this diagram<br>i_clk ffffffffffffffffffffffffffffffffffff |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Conclusion                                                                                                                                                                                                                  | o_led[4]                                                                           |

- Our goal will be to create a design with these outputs

- If successful, you'll see this in GTKwave

### **G** State Transition

```

Lesson Overview

▷ LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

Past Operator

Formal Verification

SymbiYosys Tasks

Exercise

Bonus

Conclusion

```

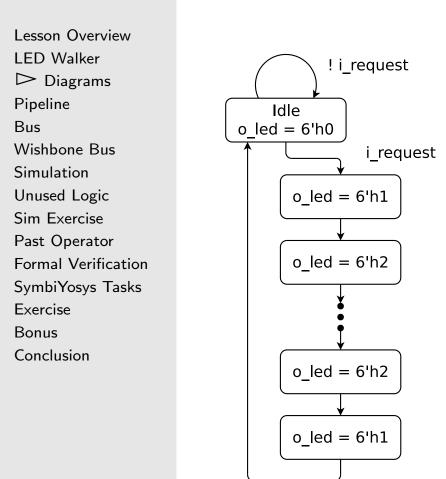

The key to this design is the idle state

- The design waits in state 0 for an i\_request

- Only responds when it isn't busy

```

initial state = 0;

always @(posedge i_clk)

if ((i_request)&&(!o_busy))

state <= 4'h1;

else if (state >= 4'hB)

state <= 4'h0;

else if (state != 0)

state <= state + 1'b1;

assign o_busy = (state != 0);

```

### **G** State Transition Diagrams

- States

- Shown as named bubbles

- Moore FSM: states include outputs

This FSM is a Moore FSM

- Transitions

- Arrows between states

- May contain transition criteria

- Mealy FSM: transitions include outputs

# G Outputs

Lesson Overview LED Walker ▷ Diagrams Pipeline **case**(state) Bus Wishbone Bus Simulation Unused Logic Sim Exercise Past Operator Formal Verification SymbiYosys Tasks Exercise Bonus Conclusion // ...

We can use a **case** statement for our outputs

```

always @(posedge i_clk)

4'h1: o_led <= 6'b00_0001;

4'h2: o_{led} <= 6'b00_{0010};

4'h3: o_{led} <= 6'b00_{0100};

4'h4: o_led <= 6'b00_1000;

4'h5: o_led <= 6'b01_0000;

4'h6: o_{led} <= 6'b10_{000};

4'h7: o_led <= 6'b01_0000;

4'ha: o_{led} <= 6'b00_{0010};

4'hb: o_led <= 6'b00_0001;

default: o_led <= 6'b00_0000;

endcase

```

Or can we? Does this work?

### **G** Pipeline Strategies

```

Lesson Overview

LED Walker

Diagrams

▷ Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

Past Operator

Formal Verification

SymbiYosys Tasks

Exercise

Bonus

```

Conclusion

Several approaches to pipeline logic

1. Apply the logic on every clock

### **G** Pipeline Strategies

```

Lesson Overview

LED Walker

Diagrams

▷ Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

Past Operator

Formal Verification

SymbiYosys Tasks

Exercise

Bonus

Conclusion

```

### Several approaches to pipeline logic

- 1. Apply the logic on every clock

- 2. Wait for a clock enable (CE) signal

### **G** Pipeline Strategies

```

Lesson Overview

LED Walker

Diagrams

▷ Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

Past Operator

Formal Verification

SymbiYosys Tasks

Exercise

Bonus

Conclusion

```

### Several approaches to pipeline logic

- 1. Apply the logic on every clock

- 2. Wait for a clock enable (CE) signal

- 3. Move on a request, but only when not busy

```

// Today's logic: Wait for the request

always @(posedge i_clk)

if ((i_request)&&(!o_busy))

state <= 4'h1;

else if (state >= 4'hB)

state <= 4'h0;

else if (state != 0)

state <= state + 1'b1;</pre>

```

Above: A mix of pipeline and state machine logic

This is fairly common

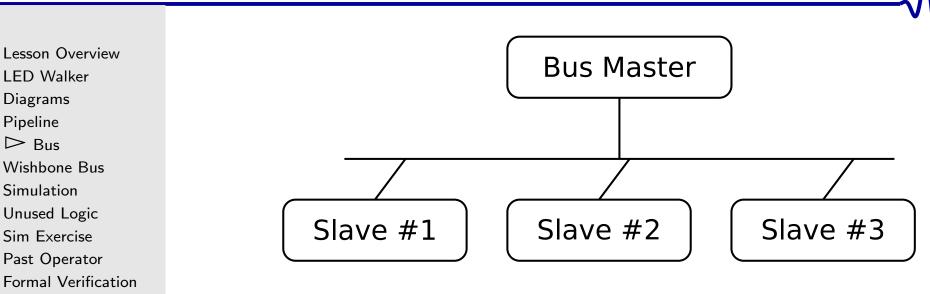

## GT Bus

Lesson Overview LED Walker Diagrams Pipeline ▷ Bus Wishbone Bus Simulation Unused Logic Sim Exercise Past Operator Formal Verification SymbiYosys Tasks Exercise Bonus Conclusion

### Interface standards simplify plugging things in

A bus interface can be standardized

- A master makes requests

A slave responds

- Read request

- Contains an address

- Slave responds with a value

- Write request

- Contains an address

- Contains a value

- Slave responds with an acknowledgment

## **G** Bus Topology

SymbiYosys Tasks

Exercise Bonus

Conclusion

- Every bus has a master

- A Bus may have many slaves

Slaves are differentiated by their address

- All connected via an *interconnect*

- A slave on one bus may be a master on another

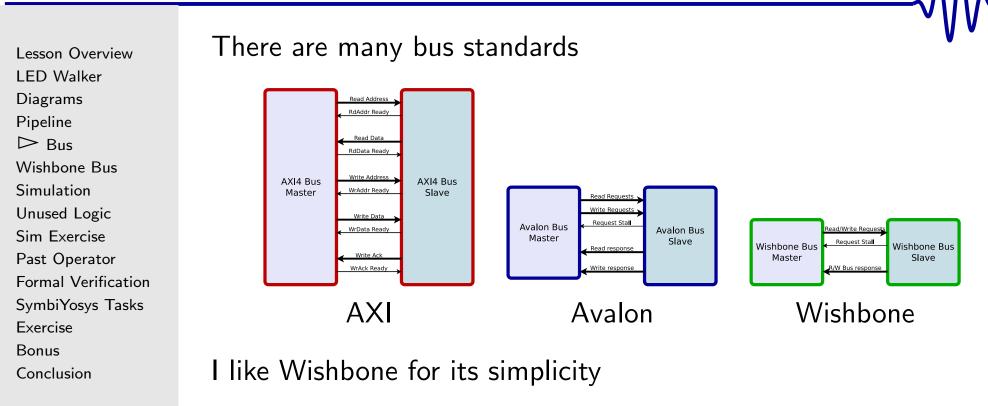

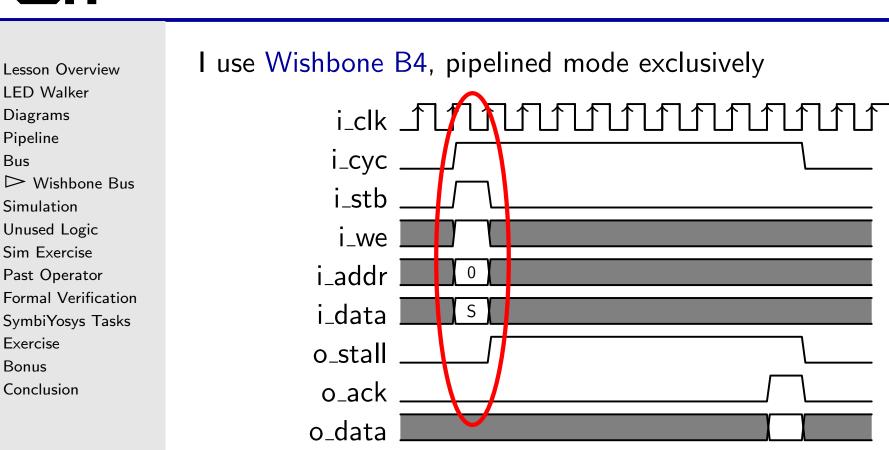

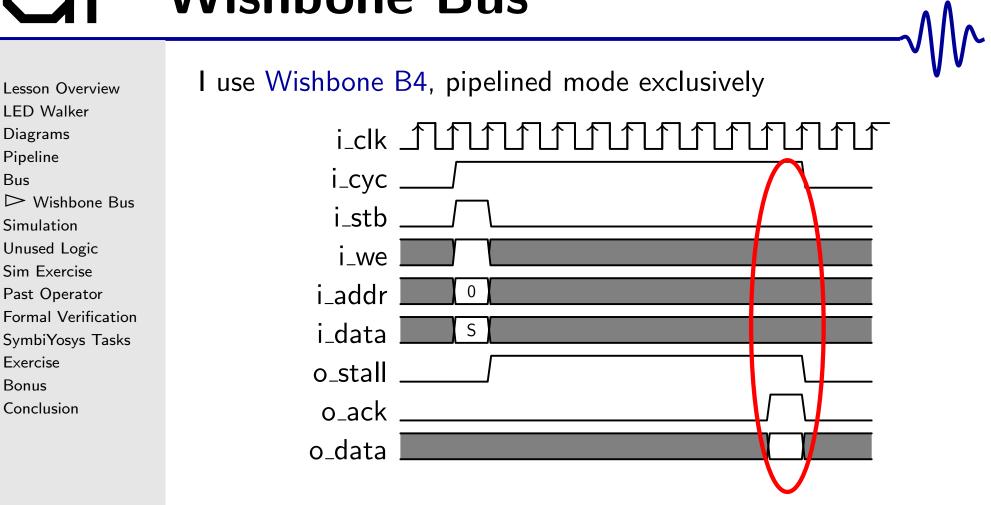

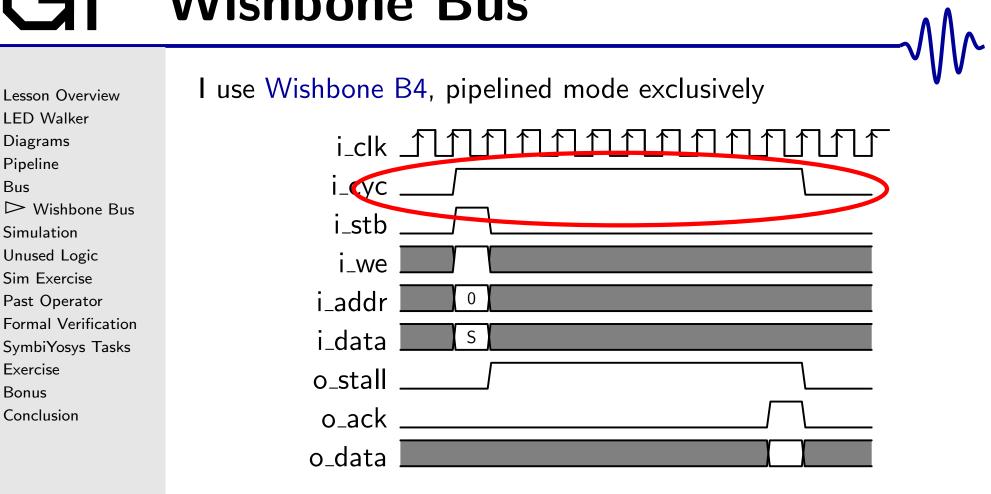

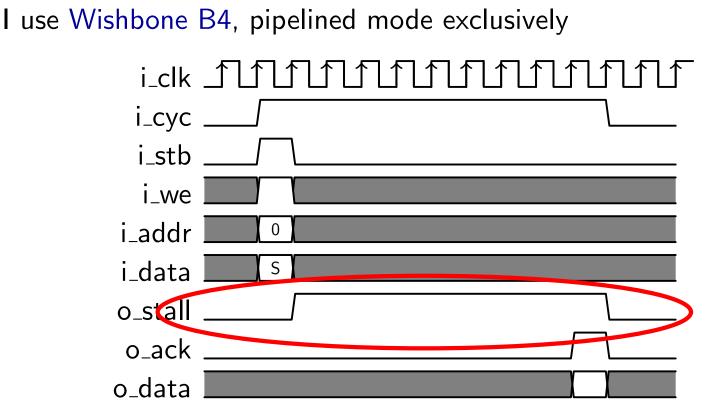

### G Many Bus Standards

- Only one request channel AXI has three, Avalon has two

- Only the request channel can stall

- Acknowledgements are simple

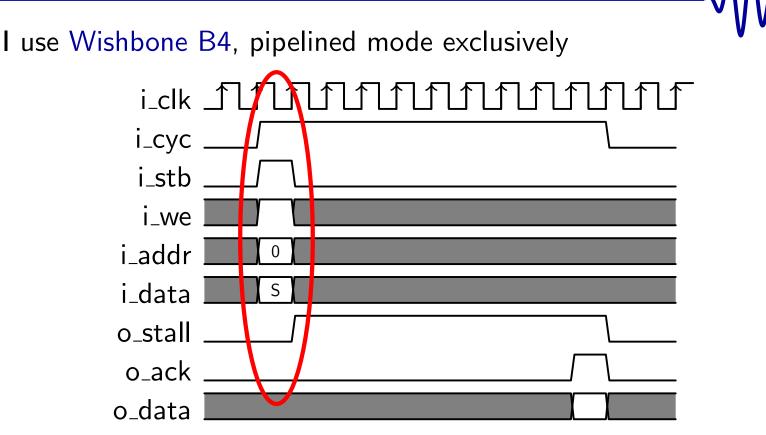

- A request takes place any time (i\_stb)&&(!o\_stall) Just like our (i\_request)&&(!o\_busy)

- The request details are found in i\_we, i\_addr, and i\_data

- These wires are don't care if i\_stb isn't true

Bus

- If i\_we, this is a write request

- A write request writes i\_data to address i\_addr

- Read requests ignore i\_data

• The response is signaled when o\_ack is true

If this was a read request, o\_data would have the result

- i\_cyc will be true from request to ack

- □ i\_stb will never be true unless i\_cyc

- A slave must respond to every request

- Multiple requests can be made before the slave responds

- This is controlled by the o\_stall signal

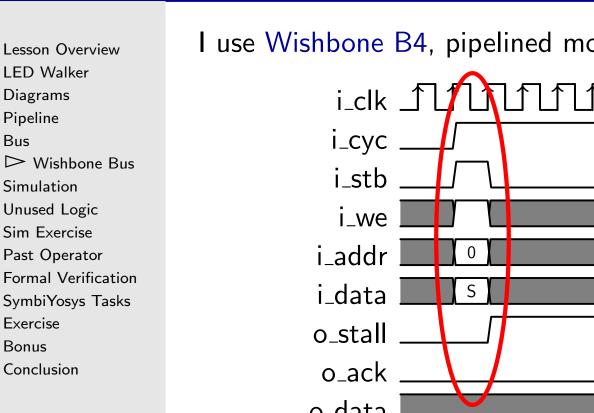

#### Lesson Overview LED Walker Diagrams Pipeline Bus ▷ Wishbone Bus Simulation Unused Logic Sim Exercise Past Operator Formal Verification SymbiYosys Tasks Exercise Bonus Conclusion

### Let's Wishbone enable our core

- We'll start the LED cycling on a write

- Writes will stall if the LED's are busy

- Return our state on a read

- We'll also acknowledge all requests immediately

Lesson Overview LED Walker Diagrams Pipeline Bus  $\triangleright$  Wishbone Bus Simulation **Unused Logic** Sim Exercise Past Operator Formal Verification SymbiYosys Tasks Exercise Bonus Conclusion

We'll immediately acknowledge any transaction

Stall if we're busy and another cycle is requested

assign  $o_stall = (busy)\&\&(i_we);$

Return state upon any read

**assign** o\_data =  $\{28'h0, state\};$

### **G** Simulation

| Lesson Overview<br>LED Walker<br>Diagrams                                  | It helps to be able to communicate with your wishbone slave during simulation                                                              |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Pipeline<br>Bus<br>Wishbone Bus<br>▷ Simulation<br>Unused Logic            | <ul> <li>Makes simulations easier</li> <li>Transaction scripting makes more sense</li> <li>Just need to implement two functions</li> </ul> |

| Sim Exercise<br>Past Operator                                              | <ul> <li>One to read from the bus</li> </ul>                                                                                               |

| Formal Verification<br>SymbiYosys Tasks<br>Exercise<br>Bonus<br>Conclusion | unsigned wb_read(unsigned a);                                                                                                              |

|                                                                            | <ul> <li>One to write to the bus</li> </ul>                                                                                                |

|                                                                            | <pre>void wb_write(unsigned a, unsigned v);</pre>                                                                                          |

We'll come back later and create high-throughput versions of these

### Sim Read

}

Lesson Overview LED Walker Diagrams Pipeline Bus Wishbone Bus  $\triangleright$  Simulation Unused Logic Sim Exercise Past Operator Formal Verification SymbiYosys Tasks Exercise Bonus Conclusion

```

unsigned wb_read(unsigned a) {

tb \rightarrow i_cyc = tb \rightarrow i_stb = 1;

tb -> i_we = 0;

tb \rightarrow i_a ddr = a;

// Make the read request

while (tb -> o_stall)

tick(tb);

tick(tb);

tb -> i_{-}stb = 0;

// Wait for the ACK

while (!tb -> o_ack)

tick(tb);

// Idle the bus, and read the response

tb -> i_cyc = 0;

return tb->o_data;

```

### G Sim Write

Lesson Overview LED Walker Diagrams Pipeline Bus Wishbone Bus ▷ Simulation Unused Logic Sim Exercise Past Operator Formal Verification SymbiYosys Tasks Exercise Bonus Conclusion

```

void wb_write(unsigned a, unsigned v) {

tb \rightarrow i_cyc = tb \rightarrow i_stb = 1;

tb -> i_we = 1;

tb->i_addr= a;

tb->i_data= v;

// Make the write request

while (tb -> o_stall)

tick(tb);

tick(tb);

tb -> i_{-}stb = 0;

// Wait for the acknowledgement

while (!tb -> o_ack)

tick(tb);

// Idle the bus and return

tb -> i_{-}cyc = 0;

```

## **G** Run Twice

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

▷ Simulation

Unused Logic

Sim Exercise

Past Operator

Formal Verification

SymbiYosys Tasks

Exercise

Bonus

Conclusion

```

This makes building the sim easy!

Let's tell our LED's to cycle twice

```

int main(int argc, char **argv) {

// Setup Verilator (same as before)

// Read from the current state

printf("Initial_state_is:0x\%02x\n",

wb_read(0);

for(int cycle=0; cycle<2; cycle++) {</pre>

// Wait five clocks

for(int i=0; i<5; i++)</pre>

tick();

// Start the LEDs cycling

wb_write(0,0);

tick();

// ... (next page)

```

### G Display State

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

▷ Simulation

Unused Logic

Sim Exercise

Past Operator

Formal Verification

SymbiYosys Tasks

Exercise

Bonus

Conclusion

```

This makes building the sim easy!

Here's the other half

The full example code is available on line

### G Unused Logic

Lesson Overview LED Walker Diagrams Pipeline Bus Wishbone Bus Simulation ▷ Unused Logic Sim Exercise Past Operator Formal Verification SymbiYosys Tasks Exercise Bonus Conclusion

% verilator --trace -Wall -cc reqwalker.v %Warning-UNUSED: reqwalker.v:37: Signal is not used: i\_cyc %Warning-UNUSED: reqwalker.v:38: Signal is not used: i\_addr %Warning-UNUSED: reqwalker.v:39: Signal is not used: i\_data %Error: Exiting due to 3 warning(s) %Error: Command Failed /usr/bin/verilator\_bin --trace -Wall -cc reqwalker.v %

What happened?

## G Unused Logic

| Lesson Overview     |

|---------------------|

| LED Walker          |

| Diagrams            |

| Pipeline            |

| Bus                 |

| Wishbone Bus        |

| Simulation          |

| ⊳ Unused Logic      |

| Sim Exercise        |

| Past Operator       |

| Formal Verification |

| SymbiYosys Tasks    |

| Exercise            |

| Bonus               |

| Conclusion          |

|                     |

### What happened?

- The -Wall flag to Verilator looks for all kinds things you might not have meant

- It turns warnings into errors

- It found logic we weren't using: i\_cyc, i\_addr, and i\_data

- These are standard bus interface wires

- I often include them, even if not used, to keep the interface standardized

- So how do get our design to work?

## G Unused Logic

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

Simulation

▷ Unused Logic

Sim Exercise

Past Operator

Formal Verification

SymbiYosys Tasks

Exercise

Bonus

Conclusion

```

Getting Verilator to ignore unused logic

Use the // Verilator lint\_off UNUSED command

Verilator will now no longer check if unused is used or not

### **G** Sim Exercise

| Lesson Overview     |

|---------------------|

| LED Walker          |

| Diagrams            |

| Pipeline            |

| Bus                 |

| Wishbone Bus        |

| Simulation          |

| Unused Logic        |

| ▷ Sim Exercise      |

| Past Operator       |

| Formal Verification |

| SymbiYosys Tasks    |

| Exercise            |

| Bonus               |

| Conclusion          |

|                     |

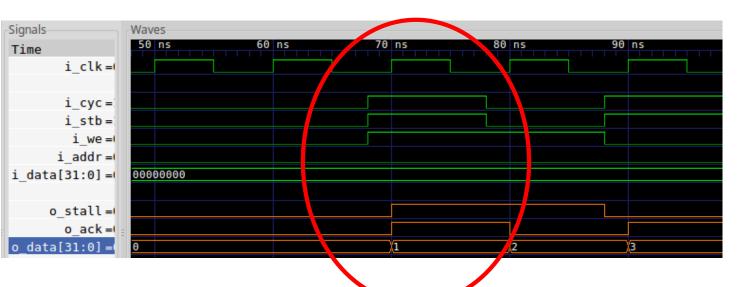

### Build and run the demo

- Examine the trace

- Examine the output

Does it work like you expected?

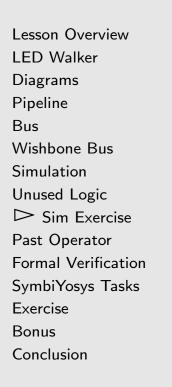

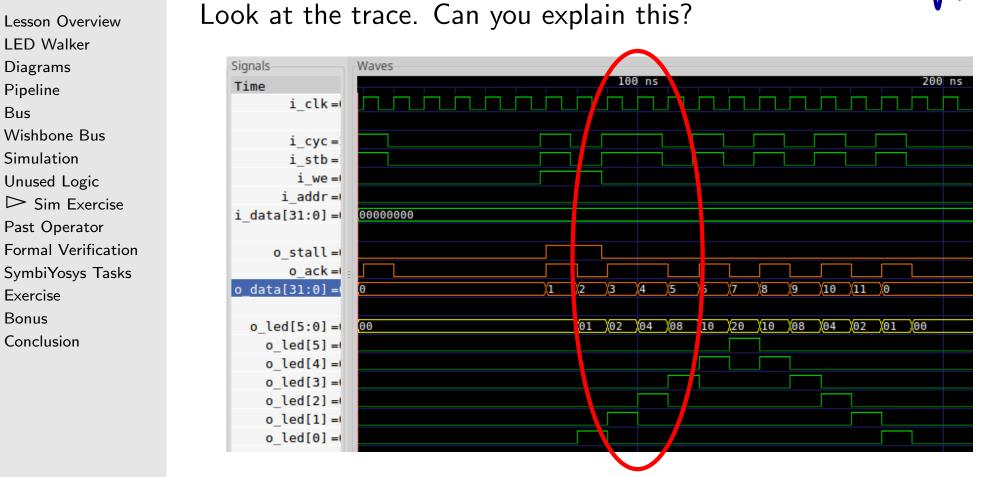

# **G**<sup>T</sup> Trace bias

### Look at the trace. Can you explain this?

Our inputs aren't clock synchronous!

- Normally, all logic changes on the posedge of i\_clk

- □ i\_cyc, i\_stb, i\_we are changing before the clock

## G Trace bias

Lesson Overview LED Walker Diagrams Pipeline Bus Wishbone Bus Simulation Unused Logic ▷ Sim Exercise Past Operator Formal Verification SymbiYosys Tasks Exercise Bonus Conclusion This is a consequence of our trace() function

We set our input values, i\_cyc, etc before calling tick()

```

void tick(void) {

tickcount++;

```

```

tb->eval(); // Adjusted inputs are

if (tfp) // recorded here

tfp->dump(tickcount * 10 - 2);

```

```

tb->i_clk = 1;// <--- posedge i_clk

tb->eval(); // takes place here!

if (tfp)

tfp->dump(tickcount * 10);

// ...

```

## **G** Trace bias

Lesson Overview LED Walker Diagrams Pipeline Bus Wishbone Bus Simulation Unused Logic ▷ Sim Exercise Past Operator Formal Verification SymbiYosys Tasks Exercise Bonus Conclusion This is a consequence of our trace() function

We set our input values, i\_cyc, etc before calling tick()

```

void tick(void) {

tickcount++;

```

tb->eval(); // Adjusted inputs are

if (tfp) // recorded here

tfp ->dump(tickcount \* 10 - 2);

## G Trace bias

Lesson Overview LED Walker Diagrams Pipeline Bus Wishbone Bus Simulation Unused Logic ▷ Sim Exercise Past Operator Formal Verification SymbiYosys Tasks Exercise Bonus Conclusion This is a consequence of our trace() function

We set our input values, i\_cyc, etc before calling tick()

```

void tick(void) {

tickcount++;

```

tb->eval(); // Adjusted inputs are

if (tfp) // recorded here

tfp->dump(tickcount \* 10 - 2);

- The tfp->dump(tickcount\*10 -2) dumps the state of everything just before the positive edge of the clock

- This captures the changes made to i\_cyc, i\_stb, i\_we, etc., in wb\_read() and wb\_write()

- The trace accurately reflected these changes taking place before the clock edge

## **GTrace bias**

| Lesson Overview     |  |

|---------------------|--|

| LED Walker          |  |

| Diagrams            |  |

| Pipeline            |  |

| Bus                 |  |

| Wishbone Bus        |  |

| Simulation          |  |

| Unused Logic        |  |

| ▷ Sim Exercise      |  |

| Past Operator       |  |

| Formal Verification |  |

| SymbiYosys Tasks    |  |

| Exercise            |  |

| Bonus               |  |

| Conclusion          |  |

|                     |  |

This is a consequence of our trace() function

- We set our input values, i\_cyc, etc before calling tick()

- Had we done otherwise, combinatorial logic wouldn't have settled before posedge i\_clk

- Worse, the trace wouldn't make any sense

- This way, things work. Logic matches the trace.

- It just looks strange.

### **G**<sup>-</sup> Simulation output

| Lesson Overview     |  |

|---------------------|--|

| LED Walker          |  |

| Diagrams            |  |

| Pipeline            |  |

| Bus                 |  |

| Wishbone Bus        |  |

| Simulation          |  |

| Unused Logic        |  |

| ▷ Sim Exercise      |  |

| Past Operator       |  |

| Formal Verification |  |

| SymbiYosys Tasks    |  |

| Exercise            |  |

| Bonus               |  |

| Conclusion          |  |

### Is this an output you expected?

| % ./requ | valker |     |         |

|----------|--------|-----|---------|

| Initial  | state  | is: | 0 x 0 0 |

| 10:      | State  | # 4 | 0       |

| 12:      | State  | # 6 | 0-      |

| 14:      | State  | # 8 | 0-      |

| 16:      | State  | #10 | 0       |

| 27:      | State  | # 4 | 0       |

| 29:      | State  | # 6 | 0-      |

| 31:      | State  | # 8 | 0-      |

| 33:      | State  | #10 | 0       |

| %        |        |     |         |

Let's look at the trace again!

# G Double ACKs

• Why are we getting two acks in a row?

We never created two adjacent requests!

# **Double ACKs**

Bus

The stall line depends upon i\_we

Without a call to **tb**->**eval**(), it won't update!

# G Double ACKs

Lesson Overview LED Walker Diagrams Pipeline Bus Wishbone Bus Simulation Unused Logic ▷ Sim Exercise Past Operator Formal Verification SymbiYosys Tasks Exercise Bonus Conclusion Remember how we defined o\_stall?

assign o\_stall = (busy)&&(i\_we);

- wb\_write() and wb\_read() both adjust i\_we

... without calling Verilator to give it a chance to update

o\_stall before referencing it!

- o\_stall is still updated before the clock, but not until after we used it in wb\_write() and wb\_read()

- We can fix this by calling tb->eval() to get Verilator to adjust o\_stall

# **Double ACKs**

}

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

\triangleright Sim Exercise

Past Operator

Formal Verification

SymbiYosys Tasks

Exercise

Bonus

```

Conclusion

Need to call **tb->eval**()

- o\_stall depends upon a Verilator input, i\_we

- Fixing this requires an extra call to **eval**()

- I don't normally need to do this

Both **wb\_read()** and **wb\_write()** need to be updated Example update to **wb**\_**read**():

```

unsigned wb_read(unsigned a) {

tb -> i_cyc = tb -> i_stb = 1;

tb \rightarrow i_we = 0; tb \rightarrow eval();

tb->i_addr= a;

// Make the request

// ...

```

# Exercise

| Lesson Overview              | Rebuild ar | nd run ag | gain. | ls this         |

|------------------------------|------------|-----------|-------|-----------------|

| LED Walker                   | 0/ /       |           |       |                 |

| Diagrams                     | % ./req    | walker    |       |                 |

| Pipeline                     | Initial    | state     | is:   | $0 \ge 0 \ge 0$ |

| Bus                          | 9:         | State     | # 2   | -0              |

| Wishbone Bus                 | 9.         | State     | # 3   | -0              |

| Simulation                   | 11:        | State     | # 5   | 0               |

| Unused Logic                 | 13:        | State     | # 7   |                 |

| Sim Exercise                 |            |           |       |                 |

| Past Operator                | 15:        | State     | # 9   | 0               |

| Formal Verification          | 17:        | State     | #11   | -0              |

| SymbiYosys Tasks<br>Exercise | 27:        | State     | # 3   | -0              |

|                              |            |           |       |                 |

| Bonus                        | 29:        | State     | # 5   | ()              |

| Conclusion                   | 31:        | State     | # 7   |                 |

|                              | 33:        | State     | # 9   | 0               |

|                              | 35:        | State     | #11   | -0              |

|                              | %          |           |       |                 |

But, why are we reading every other trace?

n - -

--0

is better?

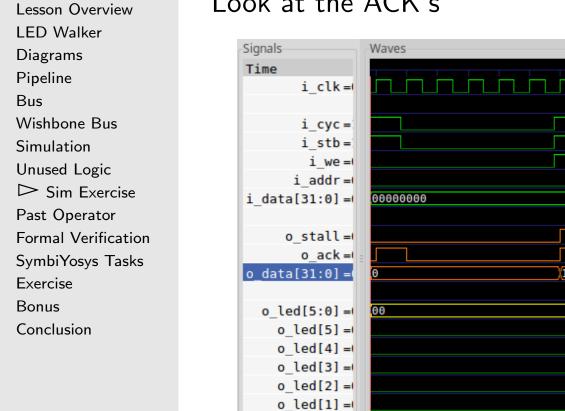

# **GT** Exercise

#### Look at the ACK's

Pattern: i\_stb, o\_ack repeats

Lesson: The clock ticks twice per read

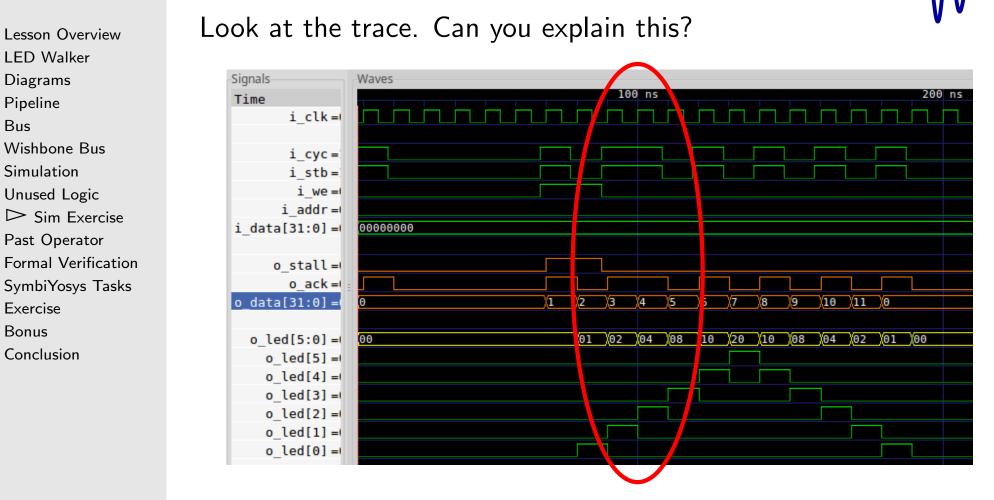

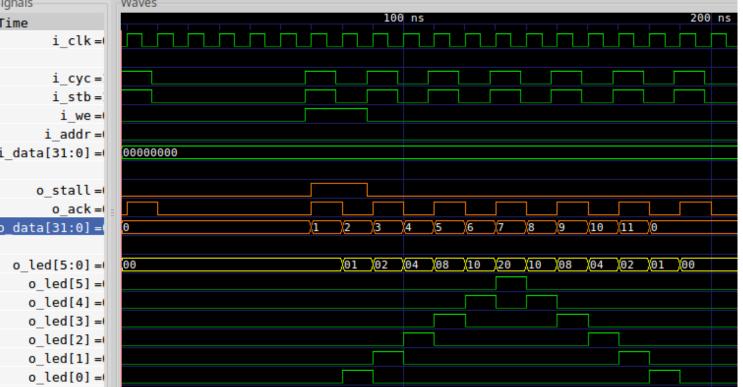

# **G** Sim Exercise

#### Here's the full and final simulation

Here you can see both LED walks, as expected

#### **G** Formal past operator

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

▷ Past Operator

Formal Verification

SymbiYosys Tasks

Exercise

Bonus

Conclusion

```

Pipeline logic needs to reason in passing time

- **\$past(X)** returns the value of X one clock ago

- **\$past**(X,N) returns the value of X N clocks ago

Both require a clock

```

always @(posedge i_clk)

if ($past(C))

assert(X == Y);

```

It's illegal to use **\$past**(X) without a clock

```

// This is an error: there's no clock

always @(*)

if ($past(C))

assert(X);

```

#### **G** Formal past operator

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

▷ Past Operator

Formal Verification

SymbiYosys Tasks

Exercise

Bonus

```

Conclusion

#### **\$past**(X) has one disadvantage

- On the initial clock, **\$past**(X) is undefined

- Assertions referencing **\$past**(X) will always fail

- Assumptions referencing **\$past**(X) will always succeed

- I guard against this with f\_past\_valid

```

reg f_past_valid;

initial f_past_valid = 0;

always @(posedge i_clk)

f_past_valid = 1'b1;

```

$\hfill\square$  To use, place f\_past\_valid in an if condition

Lesson Overview LED Walker Diagrams Pipeline Bus Wishbone Bus Simulation Unused Logic Sim Exercise Past Operator Formal  $\triangleright$  Verification SymbiYosys Tasks Exercise Bonus Conclusion

What properties might we use?

- assume properties of the inputs

- assert properties of local states and outputs

| Lesson Overview              | What properties might we use? |

|------------------------------|-------------------------------|

| LED Walker<br>Diagrams       | i_clk_ᡗᡗᡗᡗᡗᡗᡗᡗ                |

| Pipeline                     |                               |

| Bus                          | i_stb/ \                      |

| Wishbone Bus                 | bucy.                         |

| Simulation                   | busy                          |

| Unused Logic                 | o_led[0]                      |

| Sim Exercise                 |                               |

| Past Operator                | o_led[1]/ \                   |

| Formal<br>Verification       | o_led[2]                      |

| SymbiYosys Tasks<br>Exercise | o_led[3]                      |

| Bonus                        |                               |

| Conclusion                   | o_led[4]/ \                   |

| Conclusion                   | o_led[5]                      |

|                              | state 0 1 2 3 4 5 6           |

The goal waveform diagram should give you an idea

| ↑ | ↑ | ↑

8

7

9

10

11

0

What properties might we use?

For our state machine П

```

Pipeline

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

Past Operator

Formal

\triangleright Verification

SymbiYosys Tasks

Exercise

endcase

Conclusion

```

Lesson Overview

LED Walker

Diagrams

Bus

Bonus

```

always Q(*)

case(state)

4'h0: assert(o_led == 0);

4'h1: assert(o_led == 6'h1);

4'h2: assert(o_led == 6'h2);

4'hb: assert(o_led == 6'h1);

always Q(*)

assert(busy != (state == 0));

always Q(*)

assert(state <= 4'hb);</pre>

```

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

Past Operator

Formal

▷ Verification

SymbiYosys Tasks

Exercise

Bonus

```

Conclusion

```

What properties might we use?

```

- For our state machine, using \$past(X)

- An accepted write should start our cycle

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

Past Operator

Formal

▷ Verification

SymbiYosys Tasks

Exercise

Bonus

```

Conclusion

What properties might we use?

During the cycle, the state should increment

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

Past Operator

Formal

\triangleright Verification

SymbiYosys Tasks

Exercise

Bonus

Conclusion

```

What properties might we use?

For our bus interface?

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

Past Operator

Formal

\triangleright Verification

SymbiYosys Tasks

Exercise

Bonus

Conclusion

```

What properties might we use?

```

For our bus interface?

```

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

Past Operator

Formal

▷ Verification

SymbiYosys Tasks

Exercise

```

Bonus

Conclusion

What properties might we use?

• For our bus interface?

#### **G**<sup>T</sup> Cover Property

Lesson Overview LED Walker Diagrams Pipeline Bus Wishbone Bus Simulation Unused Logic Sim Exercise Past Operator Formal  $\triangleright$  Verification SymbiYosys Tasks Exercise Bonus Conclusion

#### You can also use **\$past** with **cover**

### **G** SymbiYosys Tasks

| Lesson Overview                                                           | C            |

|---------------------------------------------------------------------------|--------------|

| LED Walker                                                                |              |

| Diagrams                                                                  |              |

| Pipeline                                                                  | _            |

| Bus                                                                       |              |

| Wishbone Bus                                                              |              |

| Simulation                                                                |              |

| Unused Logic                                                              |              |

| •                                                                         |              |

| Sim Exercise                                                              |              |

| Sim Exercise<br>Past Operator                                             | Y            |

|                                                                           | Y            |

| Past Operator<br>Formal Verification<br>SymbiYosys                        | Ŷ            |

| Past Operator<br>Formal Verification<br>SymbiYosys<br>▷ Tasks             | Y            |

| Past Operator<br>Formal Verification<br>SymbiYosys                        | <b>Y</b>     |

| Past Operator<br>Formal Verification<br>SymbiYosys<br>▷ Tasks             | <b>Y</b>     |

| Past Operator<br>Formal Verification<br>SymbiYosys<br>▷ Tasks<br>Exercise | <b>Y</b><br> |

Constantly editing our SymbiYosys file is getting old

- Running cover, then

- Editing our script, then

- Running induction, then ...

- Can we do this with one file?

- Yes, using SymbiYosys tasks!

- SymbiYosys allows us to define multiple different scripts ...all in the same file

- It does this using tasks

# **G** SymbiYosys Tasks

| Lesson Overview                               | Let's define two tasks                                             |

|-----------------------------------------------|--------------------------------------------------------------------|

| LED Walker<br>Diagrams<br>Pipeline<br>Bus     | <ul> <li>cvr to run cover</li> <li>prf to run induction</li> </ul> |

| Wishbone Bus<br>Simulation                    | SymbiYosys lines prefixed by a task name are specific to that task |

| Unused Logic<br>Sim Exercise<br>Past Operator | [tasks]                                                            |

| Formal Verification<br>SymbiYosys             | prf<br>cvr                                                         |

| ➢ Tasks<br>Exercise<br>Panus                  | [options]                                                          |

| Bonus<br>Conclusion                           | cvr: mode cover                                                    |

|                                               | prf: <b>mode</b> prove                                             |

The full reqwalker.sby file is with the course handouts

#### **G** SymbiYosys Tasks

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

Past Operator

Formal Verification

SymbiYosys

▷ Tasks

Exercise

Bonus

```

Conclusion

We can now run a named task

% sby -f reqwalker.sby prf

#### ... or all tasks in sequence

% sby -f reqwalker.sby

# SymbiYosys Tasks

|                                              | - n |     |

|----------------------------------------------|-----|-----|

| Lesson Overview                              |     | use |

| LED Walker                                   |     |     |

| Diagrams                                     |     | l   |

| Pipeline                                     |     |     |

| Bus                                          |     | C   |

| Wishbone Bus                                 |     |     |

| Simulation                                   |     | _   |

| Unused Logic                                 |     |     |

| Sim Exercise                                 |     |     |

| Past Operator                                |     |     |

| Formal Verification<br>SymbiYosys<br>▷ Tasks |     |     |

| Exercise                                     |     | S   |

| Bonus                                        |     |     |

| Conclusion                                   |     |     |

#### e this often with the ZipCPU

- Jsing the yosys command hierarchy I can describe multiple configurations to verify

- With/Without the pipeline

- With/Without the instruction cache

- With/Without the data cache ..., etc.

- SymbiYosys tasks are very useful!

# GT Exercise

Lesson Overview LED Walker Diagrams Pipeline Bus Wishbone Bus Simulation Unused Logic Sim Exercise Past Operator Formal Verification SymbiYosys Tasks ▷ Exercise Bonus Conclusion Your turn! Formally verify this design

- Build and create a SymbiYosys script

- Apply to the example design

- Adjust the design until it passes

- Did you find any bugs?

- Why weren't these bugs caught in simulation?

# **GTExercise**

| Lesson Overview     |

|---------------------|

| LED Walker          |

| Diagrams            |

| Pipeline            |

| Bus                 |

| Wishbone Bus        |

| Simulation          |

| Unused Logic        |

| Sim Exercise        |

| Past Operator       |

| Formal Verification |

| SymbiYosys Tasks    |

| ▷ Exercise          |

| Bonus               |

| Conclusion          |

Your turn to design

- Add the integer clock divider to this design

- (Otherwise you'd never see the LED's change on real hardware)

- Adjust both simulator and formal properties

- Create a simulation trace

- Create a cover trace

- Do they match?

# G Bonus

```

Lesson Overview

LED Walker

Diagrams

Pipeline

Bus

Wishbone Bus

Simulation

Unused Logic

Sim Exercise

Past Operator

Formal Verification

SymbiYosys Tasks

Exercise

▷ Bonus

Conclusion

```

Bonus: If you have hardware with more than one LED ...

- Adjust the number of LED's to match your hardware

- Create an i\_btn input and connect it to a button

Replace the i\_stb input with the logic below

# G Bonus

| Lesson Overview     |

|---------------------|

| LED Walker          |

| Diagrams            |

| Pipeline            |

| Bus                 |

| Wishbone Bus        |

| Simulation          |

| Unused Logic        |

| Sim Exercise        |

| Past Operator       |

| Formal Verification |

| SymbiYosys Tasks    |

| Exercise            |

| ⊳ Bonus             |

| Conclusion          |

|                     |

Bonus: If you have hardware with more than one LED

- Adjust the number of LED's to match your hardware

- Create an i\_btn input and connect it to a button

- Replace the i\_stb input with the given logic

- Tie i\_we high

- Ignore o\_stall, i\_cyc, etc.

- You'll need to adjust the formal properties You should still be able to simulate it

- Simulate this updated design

- Implement it on your hardware

- Did it do what you expected? Why or why not?

- Does the LED walk back and forth when you press the button?

- It should!

- It might not work reliably ... yet

# G Conclusion

| Lesson Overview     |

|---------------------|

| LED Walker          |

| Diagrams            |

| Pipeline            |

| Bus                 |

| Wishbone Bus        |

| Simulation          |

| Unused Logic        |

| Sim Exercise        |

| Past Operator       |

| Formal Verification |

| SymbiYosys Tasks    |

| Exercise            |

| Bonus               |

| Conclusion          |

|                     |

What did we learn this lesson?

- Pipeline handshaking, i\_request && !o\_busy

- State transition diagrams

- Definition of a bus

- Logic involved in processing the wishbone bus

- How to make a wishbone slave

- $\hfill\square$  How to make wishbone bus calls from your Verilator C++ driver

- How to ignore unused logic in Verilator

- Verilator requires a call to eval() for combinatorial logic to settle

- The **\$past** operator in formal verification

- SymbiYosys tasks